# Microprocessors and Microcontrollers (EE-231)

Lecture-17

## Main Objectives

- Direct Memory Access

- 8237 DMA controller

- Bus interface

#### CAR

- The current address register holds a 16-bit memory address used for the DMA transfer.

- each channel has its own current address register for this purpose

- When a byte of data is transferred during a DMA operation, CAR is either incremented or decremented.

- depending on how it is programmed

#### CWCR

- The current word count register programs a channel for the number of bytes (up to 64K) transferred during a DMA action.

- The number loaded into this register is one less than the number of bytes transferred.

- for example, if a 10 is loaded to CWCR, then 11 bytes are transferred

- BA & BWC

- The base address (BA) and base word count (BWC) registers are used when auto-initialization is selected for a channel.

- In auto-initialization mode, these registers are used to reload the CAR and CWCR after the DMA action is completed.

- allows the same count and address to be used to transfer data from the same memory area

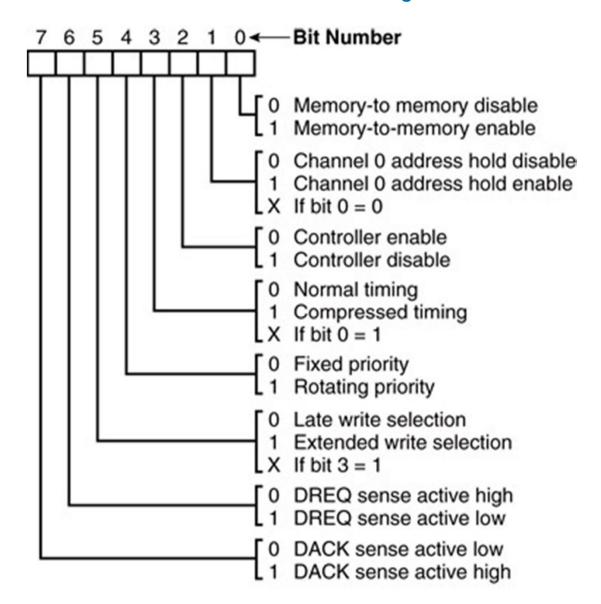

- CR

- The command register programs the operation of the 8237 DMA controller.

- Memory to memory transfer:

- The register uses bit position 0 to select the memory-to-memory DMA transfer mode.

- memory-to-memory DMA transfers use DMA channel 0 to hold the source address while DMA channel 1 holds the destination address

#### 8237A-5 command register.

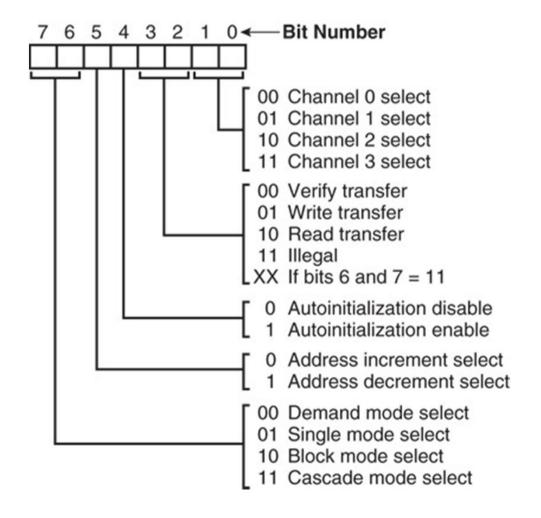

#### • MR

- The mode register programs the mode of operation for a channel.

- Each channel has its own mode register as selected by bit positions 1 and 0.

- remaining bits of the mode register select operation, auto-initialization, increment/decrement, and mode for the channel

## Three Types of DMA Mode

#### Demand mode

transfers data until DREQ becomes inactive, or when EOP pin is asserted.

#### Single mode

- releases HOLD after each byte of data is transferred

- If DREQ is active, DMAC requests a DMA transfer to microprocessor

#### Block mode

automatically transfers the number of bytes indicated by the count register for the channel

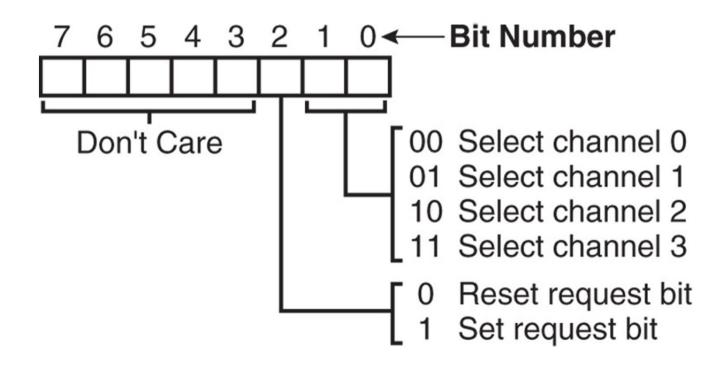

- BR

- The bus request register is used to request a DMA transfer via software.

- Very useful in memory-to-memory transfers,

where an external signal is not available to begin the DMA transfer

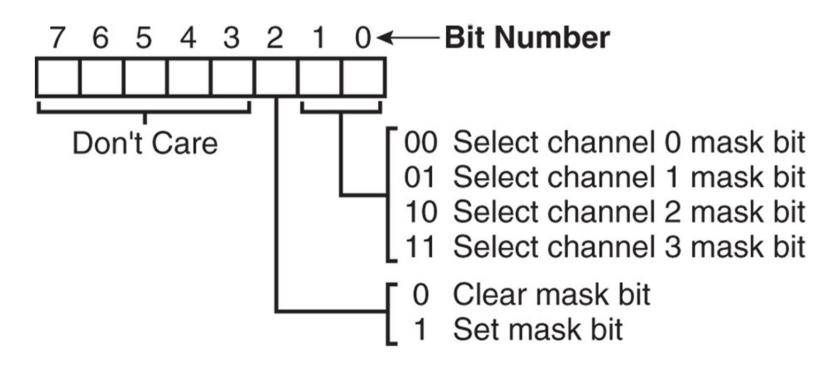

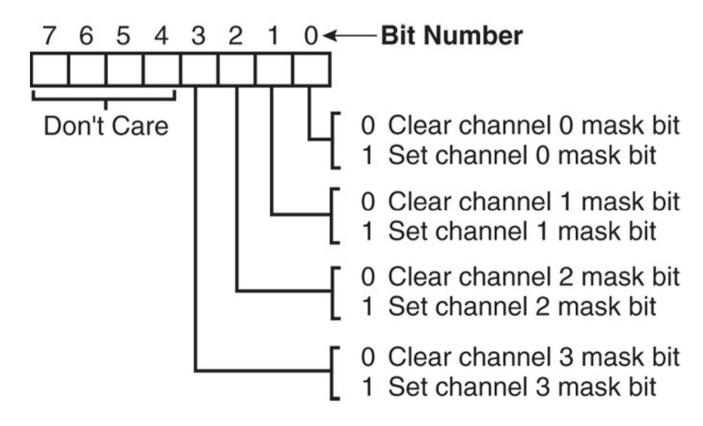

#### MRSR

- The mask register set/reset sets or clears the channel mask.

- if the mask is set, the channel is disabled.

- The RESET signal sets all channel masks to disable them

#### MSR

The mask register clears or sets all of the masks with one command instead of individual channels, as with the MRSR.

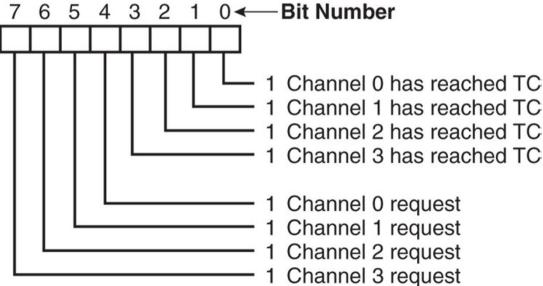

#### SR

- The status register shows status of each DMA channel. The TC bits indicate if the channel has reached its terminal count (transferred all its bytes).

- When the terminal count is reached, the DMA transfer is terminated for most modes of operation.

the request bits indicate whether the DREQ input for a given channel is active

## Software Commands

Following are the software commands to govern the operation of the DMA

| Signals |    |    |    |     |     | Onevetion                      |  |

|---------|----|----|----|-----|-----|--------------------------------|--|

| A3      | A2 | A1 | A0 | ĪŌŔ | ĪŌW | Operation                      |  |

| 1       | 0  | 0  | 0  | 0   | 1   | Read Status Register           |  |

| 1       | 0  | 0  | 0  | 1   | 0   | Write Command Register         |  |

| 1       | 0  | 0  | 1  | 0   | 1   | Illegal                        |  |

| 1       | 0  | 0  | 1  | 1   | 0   | Write Request Register         |  |

| 1       | 0  | 1  | 0  | 0   | 1   | Illegal                        |  |

| 1       | 0  | 1  | 0  | 1   | 0   | Write Single Mask Register Bit |  |

| - 1     | 0  | 1  | 1  | 0   | 1   | Illegal                        |  |

| 1       | 0  | 1  | 1  | 1   | 0   | Write Mode Register            |  |

| 1       | 1  | 0  | 0  | 0   | 1   | Illegal                        |  |

| 1       | 1  | 0  | 0  | 1   | 0   | Clear Byte Pointer Flip/Flop   |  |

| 1       | 1  | 0  | 1  | 0   | 1   | Read Temporary Register        |  |

| 1       | 1  | 0  | 1  | 1   | 0   | Master Clear                   |  |

| 1       | 1  | 1  | 0  | 0   | 1   | Illegal                        |  |

| 1       | 1  | 1  | 0  | 1   | 0   | Clear Mask Register            |  |

| 1       | 1  | 1  | 1  | 0   | 1   | Illegal                        |  |

| 1       | 1  | 1  | 1  | 1   | 0   | Write All Mask Register Bits   |  |

## Software Commands

- (1)Master Clear

- Acts exactly the same as the RESET signal to the 8237.

- as with the RESET signal, this command disables all channels

- (2)Clear mask register

- Enables all four DMA channels.

- (3)Clear the first/last flip-flop

- Clears the first/last (F/L) flip-flop within 8237.

- The F/L flip-flop selects which byte (low or high order) is read/written in the current address and current count registers.

- if F/L = 0, the low-order byte is selected

- if F/L = 1, the high-order byte is selected

- Any read or write to the address or count register automatically toggles the F/L flip-flop.

## Programming the Address and Count Registers

- Figure (on next slide) shows I/O port locations for programming the count and address registers for each channel.

- The state of the F/L flip-flop determines whether the LSB or MSB is programmed.

- if the state is unknown, count and address could be programmed incorrectly

- It is important to disable the DMA channel before address and count are programmed.

#### 8237A-5 DMA channel I/O port addresses.

| Observation | B                           | Operation | Signals |        |        |    |        |        |        |                    |                  |

|-------------|-----------------------------|-----------|---------|--------|--------|----|--------|--------|--------|--------------------|------------------|

| Channel     | Register                    |           | CS      | ĪŌŔ    | ĪŌW    | A3 | A2     | A1     | A0     | Internal Flip-Flop | Data Bus DB0-DB7 |

| 0           | Base and Current Address    | Write     | 0       | 1      | 0      | 0  | 0      | 0      | 0      | 0<br>1             | A0-A7<br>A8-A15  |

|             | Current Address             | Read      | 0       | 0      | 1      | 0  | 0      | 0      | 0      | 0<br>1             | A0-A7<br>A8-A15  |

|             | Base and Current Word Count | Write     | 0       | 1<br>1 | 0      | 0  | 0      | 0      | 1      | 0<br>1             | W0-W7<br>W8-W15  |

|             | Current Word Count          | Read      | 0       | 0      | 1      | 0  | 0      | 0      | 1      | 0<br>1             | W0-W7<br>W8-W15  |

| 1           | Base and Current Address    | Write     | 0       | 1      | 0      | 0  | 0      | 1      | 0      | 0<br>1             | A0-A7<br>A8-A15  |

|             | Current Address             | Read      | 0       | 0      | 1<br>1 | 0  | 0      | 1      | 0      | 0<br>1             | A0-A7<br>A8-A15  |

|             | Base and Current Word Count | Write     | 0       | 1<br>1 | 0      | 0  | 0      | 1      | 1      | 0<br>1             | W0-W7<br>W8-W15  |

|             | Current Word Count          | Read      | 0       | 0      | 1      | 0  | 0      | 1      | 1      | 0<br>1             | W0-W7<br>W8-W15  |

| 2           | Base and Current Address    | Write     | 0       | 1      | 0      | 0  | 1      | 0      | 0      | 0<br>1             | A0-A7<br>A8-A15  |

|             | Current Address             | Read      | 0       | 0      | 1      | 0  | 1      | 0      | 0      | 0<br>1             | A0-A7<br>A8-A15  |

|             | Base and Current Word Count | Write     | 0       | 1<br>1 | 0      | 0  | 1      | 0      | 1      | 0<br>1             | W0-W7<br>W8-W15  |

|             | Current Word Count          | Read      | 0       | 0      | 1      | 0  | 1      | 0      | 1<br>1 | 0<br>1             | W0-W7<br>W8-W15  |

| 3           | Base and Current Address    | Write     | 0       | 1      | 0      | 0  | 1      | 1      | 0      | 0<br>1             | A0-A7<br>A8-A15  |

|             | Current Address             | Read      | 0       | 0      | 1      | 0  | 1      | 1      | 0      | 0<br>1             | A0-A7<br>A8-A15  |

|             | Base and Current Word Count | Write     | 0       | 1      | 0      | 0  | 1      | 1      | 1      | 0<br>1             | W0-W7<br>W8-W15  |

|             | Current Word Count          | Read      | 0       | 0      | 1      | 0  | 1<br>1 | 1<br>1 | 1      | 0<br>1             | W0-W7<br>W8-W15  |

## Basic Steps to Program

- Four steps are required to program the 8237:

- (1) The F/L flip-flop is cleared using a clear F/L command

- (2) the channel is disabled

- (3) LSB & MSB of the address are programmed

- (4) LSB & MSB of the count are programmed

- Once these four operations are performed, the channel is programmed and ready to use.

- additional programming is required to select the mode of operation before the channel is enabled and started

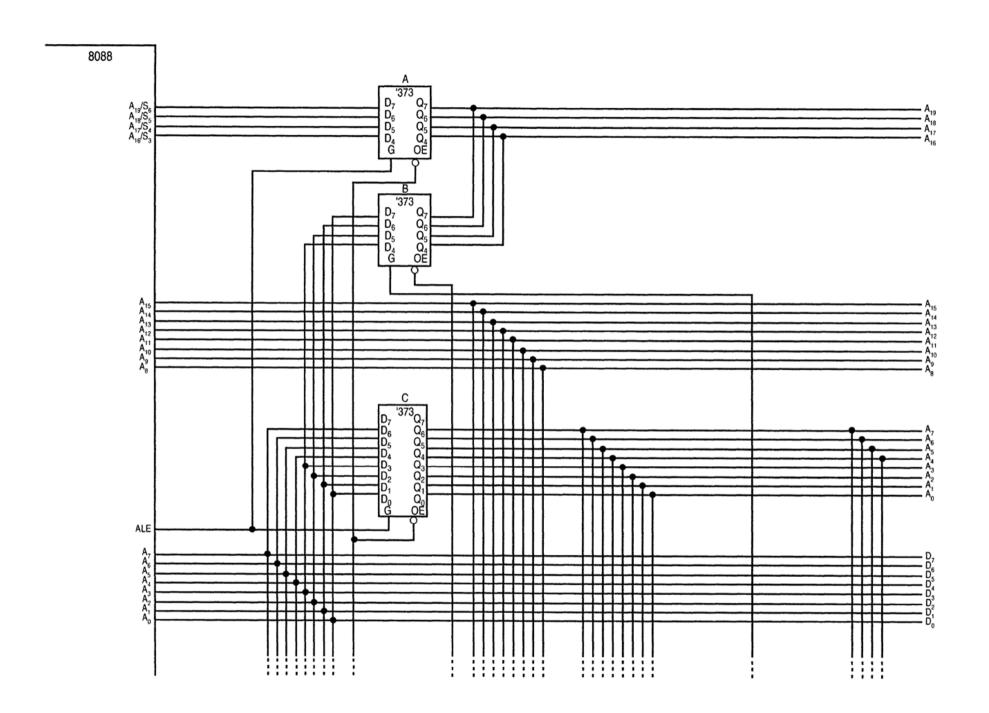

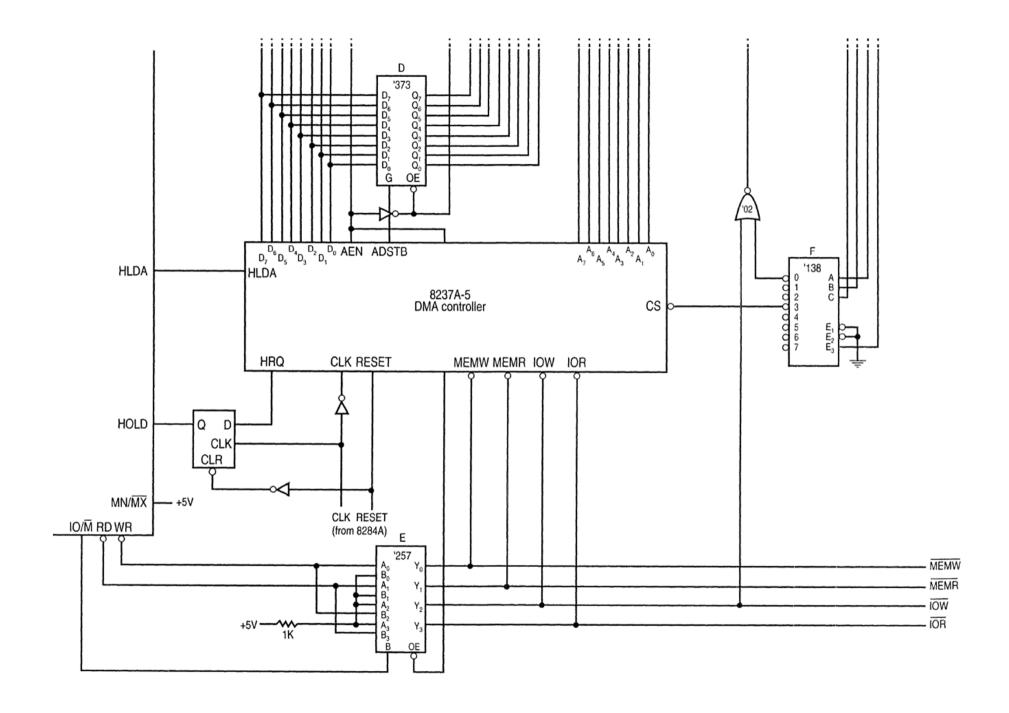

## The 8237 Connected to the 80X86

- The address enable (AEN) output of 8237 controls the output pins of the latches and outputs of the 74LS257 (E).

- during normal operation (AEN=0), latches A & C and the multiplexer (E) provide address bus bits  $A_{19}$ – $A_{16}$  and  $A_7$ – $A_0$

- The multiplexer provides the system control signals as long as the 80X86 is in control of the system.

- during a DMA action (AEN=1), latches A & C are disabled along with the multiplexer (E)

- latches D and B now provide address bits  $A_{19}$ – $A_{16}$  and  $A_{15}$ – $A_{8}$

- Address bus bits A<sub>7</sub>-A<sub>0</sub> are provided directly by the 8237 and contain part of the DMA transfer address.

- The DMA controller provides conntrol signals.

## The ISA BUS

- The Industry Standard Architecture, bus has been around since start of the IBM-PC

- since 1982

- Any card from the very first personal computer will plug in & function in any P4based system.

- provided they have an ISA slot

- ISA bus mostly gone from the home PC, but still found in many industrial applications.

- due to low cost & number of existing cards

## **Evolution of the ISA Bus**

- Over years, the ISA bus evolved from original 8-bit, to the 16-bit standard found today.

- With the P4, ISA bus started to disappear.

- a 32-bit version called the EISA bus (Extended ISA) has also largely disappeared

- What remains today is an ISA slot that can accept 8-bit ISA or 16-bit ISA cards.

- 32-bit printed circuit cards are now PCI bus

- in some older 80486 systems, VESA cards

## The 8-Bit ISA Bus Output Interface

- The ISA bus connector contains

- the demultiplexed address bus (A<sub>19</sub>–A<sub>0</sub>) for the 1M-byte 8088 system

- the 8-bit data bus  $(D_7-D_0)$

- control signals MEMR, MEMW, IOR, and IOW for controlling I/O and any memory placed on the printed circuit card

- Memory is seldom added to ISA today because ISA cards operate at only 8 MHz.

- EPROM or flash memory for setup may be on some ISA cards, but never RAM

- Other signals, useful for I/O interface, are the interrupt request lines IRO2–IRO7.

## The 8-Bit ISA Bus Output Interface

- The ISA bus connector contains

- DMA channel 0–3 control signals are also present on the connector.

- DMA request inputs are labeled DRQ1–DRQ3 and the DMA acknowledge outputs are labeled DACK0 - DACK3.

#### The 8-bit ISA bus.

- IRQ<sub>2</sub> is redirected to IRQ<sub>2</sub> on modern systems, and is so labeled here

- note the DRQ<sub>0</sub> input pin is missing,

- early PCs used DRQ<sub>0</sub> & the DACK<sub>0</sub> output as a refresh signal to refresh DRAM on the ISA card

- today, this output pin contains a 15.2  $\mu$ s clock signal used for refreshing DRAM

- remaining pins are for power and RESET

| #     |                                                                                                                                               |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| GND   | IO CHK                                                                                                                                        |

| RESET | D7                                                                                                                                            |

| +5V   | D6                                                                                                                                            |

| IRQ9  | D5                                                                                                                                            |

| -5V   | D4                                                                                                                                            |

| DRQ2  | D3                                                                                                                                            |

| -12V  | D2                                                                                                                                            |

| ows   | D1                                                                                                                                            |

| +12V  | D0                                                                                                                                            |

| GND   | IO RDY                                                                                                                                        |

| MEMW  | AEN                                                                                                                                           |

| MEMR  | A19                                                                                                                                           |

| ĪŌW   | A18                                                                                                                                           |

|       | A17                                                                                                                                           |

| DACK3 | A16                                                                                                                                           |

| DRQ3  | A15                                                                                                                                           |

| DACK1 | A14                                                                                                                                           |

|       | A13                                                                                                                                           |

| DACK0 | A12                                                                                                                                           |

|       | _A11                                                                                                                                          |

|       | A10                                                                                                                                           |

| IRQ6  | A9                                                                                                                                            |

| IRQ5  | A8                                                                                                                                            |

| IRQ4  | A7                                                                                                                                            |

| IRQ3  | A6                                                                                                                                            |

|       | A5                                                                                                                                            |

| T/C   | A4                                                                                                                                            |

| ALE   | A3                                                                                                                                            |

| +5V   | A2                                                                                                                                            |

| OSC   | A1                                                                                                                                            |

|       | GND RESET +5V IRQ9 -5V DRQ2 -12V OWS +12V GND MEMW MEMR IOW IOR DACK3 DACK3 DACK1 DRQ1 DACK0 CLOCK IRQ7 IRQ6 IRQ5 IRQ4 IRQ3 DACK2 T/C ALE +5V |

GND

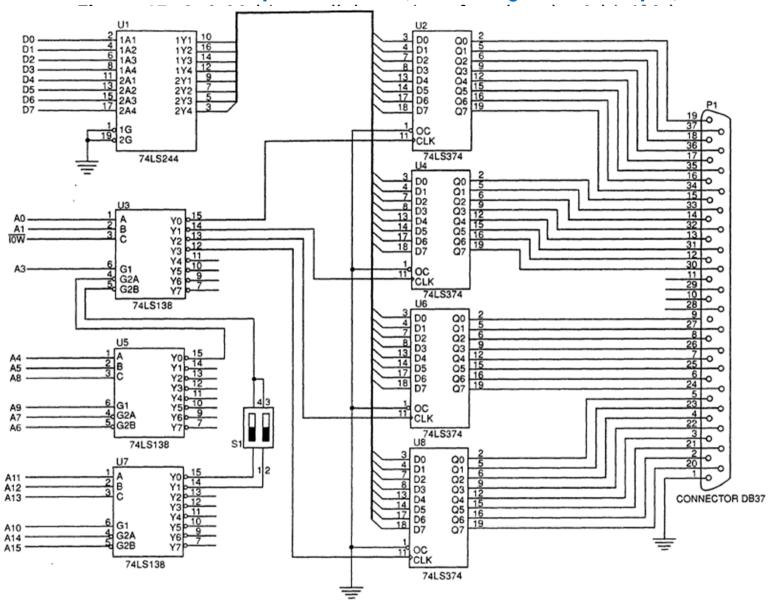

#### The 8-Bit ISA Bus Output Interface (Generating a 32-bit output)

## The 8-Bit ISA Bus Input Interface

- Figure shows an input interface to the ISA bus, using a pair of ADC804 analog-to-digital converters.

- made through a nine-pin DB<sub>9</sub> connector

- Decoding I/O port addresses is more complex, as each converter needs:

- a write pulse to start a conversion

- a read pulse to read the digital data converted

- a pulse to enable the selection of the INTR output

U1A 741S125 D0 DO 18 1Y1 16 1Y2 14 1Y3 12 1Y4 9 2Y1 7 2Y2 5 2Y3 3 2Y4 1A1 4 1A2 6 1A3 8 1A4 11 2A1 13 2A2 15 2A3 17 VI+ D0 D1 D2 D3 D4 D5 D6 D7 VI-CLKR CLK vçc 1 CS RD RD WR INTR 1G 19 VREF .001 74LS244 **≯**1κ **AGND** ADC0804 Y0 015 Y1 014 Y2 013 Y3 012 Y4 010 Y6 0 7 Y7 0 7 A0 -CONNECTOR DB9 IOW 6 4 G2A 5 G2B A2 -18 17 16 15 14 13 12 11 DB0 DB1 DB2 DB3 DB4 DB5 DB6 DB7 VI+ 74LS138 VI-CLKF 01 019 02 017 03 016 04 015 05 014 06 013 07 012 1K A3 -A5 -A6 -A7 -A8 -A9 -A10-A11-A12-1 11 2 12 3 13 4 14 5 16 6 17 8 18 9 19 11 110 CLK. CS RD WR INTR 六.001 VREF AGND ADC0804 U1B 74LS125 16L8 A13 -A14 -A15 -IOR -

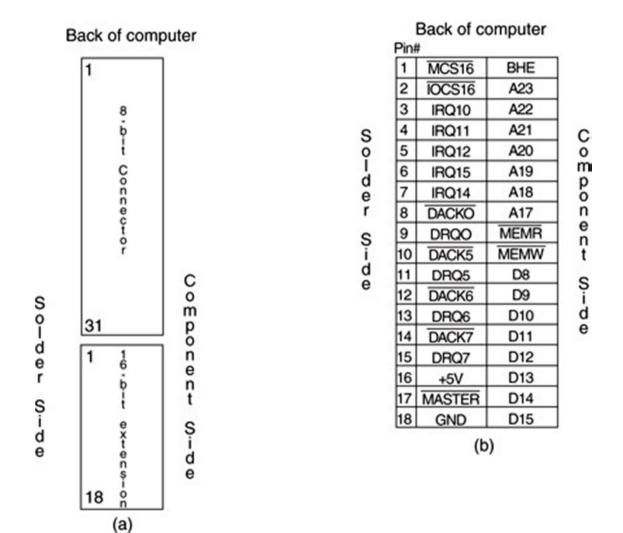

### The 16-Bit ISA Bus

- The difference between 8- & 16-bit ISA is an extra connector behind the 8-bit connector.

- A 16-bit card contains two edge connectors:

- one plugs into the original 8-bit connector

- the other plugs into the new 16-bit connector

- Figure shows pin-out and placement of the additional connector in relation to the 8-bit connector.

## The 16-bit ISA bus. (a) Both 8- and 16-bit connectors and (b) the pinout of the 16-bit connector.

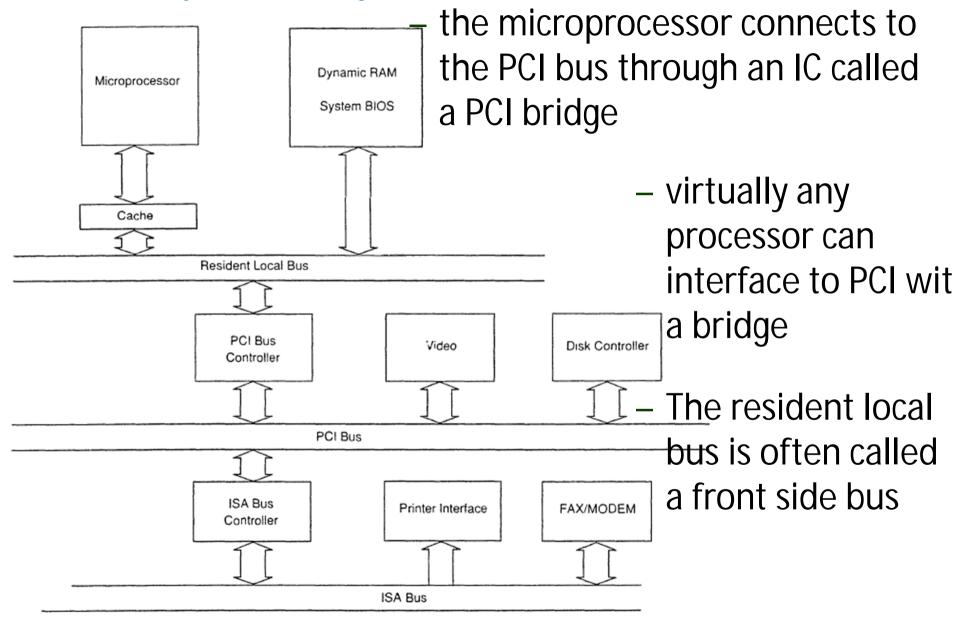

## PERIPHERAL COMPONENT INTERCONNECT (PCI) BUS

- PCI (peripheral component interconnect) is virtually the only bus found in new systems.

- ISA still exists by special order for older cards

- PCI has replaced the VESA local bus.

- PCI has plug-and-play characteristics and ability to function with a 64-bit data bus.

- A PCI interface contains registers, located in a small memory device containing information about the board.

- this allows PC to automatically configure the card

- this provides plug-and-play characteristics to the ISA bus, or any other bus

- Called plug-and-play (PnP), it is the reason PCI has become so popular.

#### System block diagram for the PC that contains a PCI bus.

## The PCI Bus Pin-Out

- PCI functions with a 32- or 64-bit data bus and a full 32-bit address bus.

- address and data buses, labeled AD<sub>0</sub>–AD<sub>63</sub> are multiplexed to reduce size of the edge connector

- A 32-bit card has connections 1 through 62, the 64-bit card has all 94 connections.

- The 64-bit card can accommodate a 64-bit address if required at some future point.

- Figure shows the PCI bus pin-out.

#### The pin-out of the PCI bus.

- PCI is most often used for I./O interface to the microprocessor

- memory could be interfaced, but with a Pentium, would operate at 33 MHz, half the speed of the Pentium resident local

- PCI 2.1 operates at 66 MHz, and 33

MHz for older interface cards

- P4 systems use 200 MHz bus speed (often listed as 800 MHz)

- there is no planned modification to the PCI bus speed yet

Component Side

AD30 +3.3V

AD28

+3.3V

AD20

GND

+3 3V

FRAME

GND

+3 3V

Notes: (1) pins 63–94 exist only on the 64-bit PCI card (2) + VI/O is 3.3V on a 3.3V board and +5V on a 5V board (3) blank pins are reserved

| C   |

|-----|

| •   |

| C   |

|     |

| п   |

| ••• |

| p   |

| -   |

| C   |

|     |

| п   |

|     |

| е   |

| n   |

|     |

| t   |

| •   |

|     |

| •   |

| S   |

| i   |

|     |

| d   |

| •   |

| е   |

| •   |

|     |

|     |

|     |

|     |

|     |

|     |

|     |

|     |

|     |

|     |

|     |

|     |

|     |

|     |

|     |

|     |

|     |

|     |

|     |

|     |

|     |

|     |

<u>580</u>

AD15

AD11

KEY

+3.3V

AD6

AD4

C/BE5

AD62

GND

AD58 GND

AD56

AD54

AD52

AD48

AD44

AD42

AD40

AD38

AD36

GND

GND

AD39

AD37

+3 3V

## The PCI Address/Data Connections

- The PCI address appears on AD<sub>0</sub>–AD<sub>31</sub> and is multiplexed with data.

- some systems have a 64-bit data bus using  $AD_{32}$ – $AD_{63}$  for data transfer only

- these pins can be used for extending the address to 64 bits

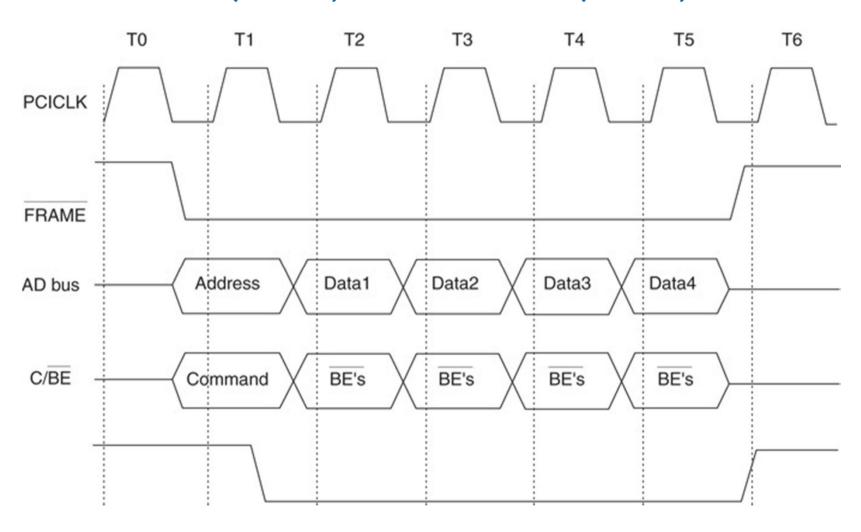

- Figure shows the PCI bus timing diagram

- which shows the address multiplexed with data and control signals used for multiplexing

The basic timing for the PCI bus system. Note that this transfers either four 32-bit numbers (32-bit PCI) or four 64-bit numbers (64-bit PCI).

## **Configuration Space**

- PCI contains a 256-byte memory to allow the PC to interrogate the PCI interface.

- this feature allows the system to automatically configure itself for the PCI plug-board

- Microsoft calls this plug-and-play (PnP)

- The first 64 bytes contain information about the PCI interface.

- The first 32-bit doubleword contains the unit ID code and the vendor ID code.

## PCI Express Bus

- The PCI Express transfers data in serial at 2.5 GHz

- 250 MBps to 8 GBps for PCI Express interfaces

- standard PCI delivers data at about 133 MBps

- Each serial connection on the PCI Express bus is called a lane.

- slots on the main board are single lane slots with a total transfer speed of 1 GBps

- A PCI Express video card connector currently has 16 lanes with a transfer speed of 4 GBps.

- The standard allows up to 32 lanes.

- at present the widest is the 16 lanes video card

- Most main boards contain four single lane slots for peripherals and one 16 lane slot for the video card.

- a few newer boards contain two 16 lane slots

- PCI Express 2 bus was released in late 2007.

- transfer speed from 250 MBps to 500 MBps, twice that of the PCI Express

- PCI is replacing most current video cards on the AGP port with the PCI Express bus.